本文共 3960 字,大约阅读时间需要 13 分钟。

ART世界探险(3) - ARM 64位CPU的架构快餐教程

前面我们说过,Dalvik如果没有JIT的话,可以做到架构无关,让Dalvik指令都解释执行。但是ART是AOT,要编译成针对芯片具体的机器指令。

所以,研究Dalvik的时候可以不用太关心目标指令,而我们研究ART必须对目前最流行的微处理器的架构有个基本的了解。在上一讲我们对于ART从java byte code到ARM64 v8指令的整个流程有了一个大概的了解之后,我们就目前最流行的ARM64位芯片的知识进行一些探索。我们的目的不是写一个操作系统,所以我们尽可能挑实用的讲。ARM架构简史

我们用NDK编译一个jni库之后会发现,生成了armeabi,armeabi-v7a,arm64-v8a三个目录。这三个目录,代表了ARM目前最流行的三种架构的指令集。

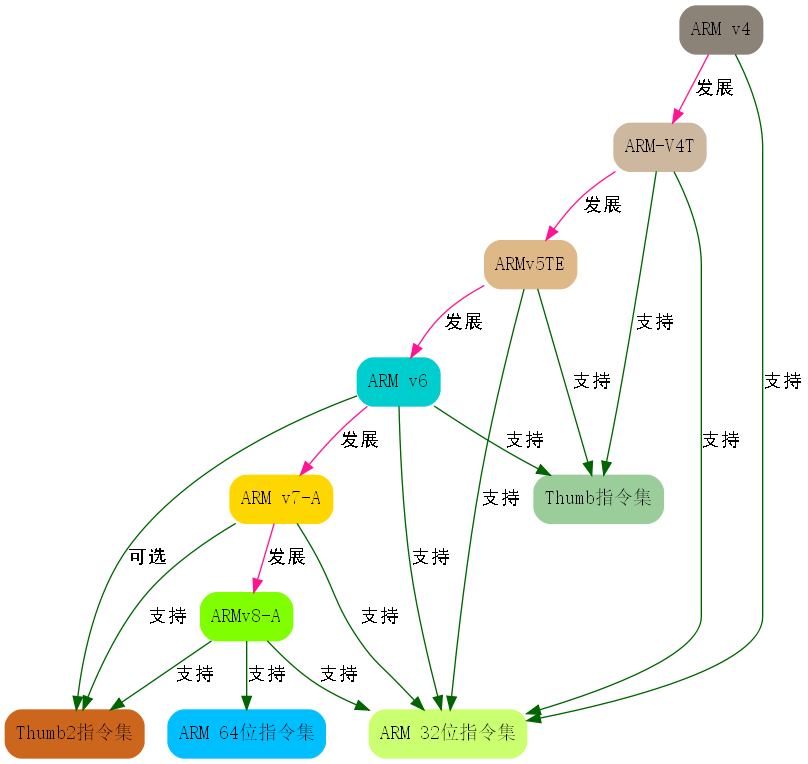

ARM芯片从1985年诞生以来,经历了主要6次大的架构调整。

- ARMv4及之前:只使用32位的ARM指令集。

- ARMv4T,在32位ARM指令集的基础上,增加了16位的Thumb指令集。这是第一个被广泛使用的架构,代表芯片ARM7TDMI和ARM9TDMI。

- ARMv5TE,增加了DSP操作,饱和算法,ARM和Thumb切换。代表芯片:ARM926EJ-S。

- ARM v6,对内存访问的架构有所调整,支持SIMD指令。代表芯片:ARM1136JF-S。这一代Thumb2成为可选项。

- ARM v7-A,将v6时可选的Thumb2指令集变成必选项,支持NEON指令。代表芯片Cortex-A8, A9, A15, A17。

- ARMv8-A,支持两种架构,64位的AArch64和AArch32。其中,AArch32跟原有的v7-A架构是基本一样的。代表芯片为A57, A53, A73, A72.

我们通常见到的armeabi,实际上对应的是ARM v4T~v6的指令。为了节省空间,我们基本上都编成16位的Thumb指令。armeabi-v7a,对应v7-A架构。arm64-v8a对应ARM v8-A的AArch64指令。

我们习惯上,把ARM v4之前就有的基础的32位ARM指令集称为A32指令集,16位的Thumb指令称为T16指令集,AArch64指令集称为A64指令集。

其中,Thumb/Thumb2和A32指令集是兼容的。Thumb和Thumb2比较节省空间,但是有些A32指令的功能是没有的。

这时候,只要从Thumb状态切换到ARM状态下就好了,执行完A32才有的指令,回去再执行T16指令就好了。

但是A64指令是不兼容Thumb的,在这种状态下,只有A64指令这一种指令可以用。

Android所用的ARM芯片简史

在Android刚出来的时候,HTC G1所用的高通MSM7201芯片,基于ARM11,用的是ARM v6指令集。

后来德州仪器的OMAP 3430第一次将Cortex-A系列的第一个架构Cortex-A8,引入现实世界中。开启了ARM v7a的时代。这个时代的代表机型就是Moto Droid/MileStone,开启了第一批百万级的Android手机。随后,从NVidia的Tegra 2开始,我们进入了A9和双核的时代。Tegra 3使用Cortex-A15,在32位上达到一个高峰。同时,以MediaTek为代表的中低端厂商开始将低端的Cortex-A7发挥到极致,MT6577是两个A7,MT6589为4个A7,MT6592是8个A7.进入64位时代的代表芯片,就是Qualcomm的SnapDragon 810芯片,4个Cortex-A57的发热问题困扰了无数厂商去年整整一年。MediaTek继续发挥低端的威力,升级成64位的Cortex-A53。MT6735芯片4个A53,MT6753芯片8个A53。幸好最近的Helix X25/20开始用A72+A53了,我们总算是在MTK芯片上见到一次大核的身影。从芯片的广泛性上考虑,我们这个讲座的目标芯片就放在Cortex-A53上。

Cortex-A57和Cortex-A53芯片对比

我们简单列一下A57与A53的对比,大家有个直观印象就好。

| Cortex-A53 | Cortex-A57 | |

|---|---|---|

| 典型时钟 | 2GHz, 28nm工艺 | 1.5~2.5GHz, 20nm工艺 |

| 执行顺序 | 顺序 | 乱序、投机问题、超标量 |

| 核心数 | 1~4 | 1~4 |

| 峰值整数能力 | 2.3MIPS/MHz | 4.1~4.76MIPS/MHz |

| 浮点单元 | 有 | 有 |

| 半精度 | 有 | 有 |

| 硬件除法 | 有 | 有 |

| 融合乘法累加 | 有 | 有 |

| 流水线 | 8级 | 15级+ |

| 返回栈条目 | 4 | 8 |

| 通用中断控制 | 外部 | 外部 |

| AMBA接口 | 64位 AMBA 4/5 | 128位 AMBA 4/5 |

| L1指令缓存 | 8K ~ 64KB | 48KB |

| L1数据缓存 | 8K ~ 64KB | 32KB |

| L2缓存 | 可选 | 集成 |

| L2缓存 | 128K~2M | 512K~2M |

| 主TLB | 512 | 1024 |

| uTLB | 10 | 48指令,32数据 |

对我们理解后续知识有影响的主要有两条:一是Cortex-A53不支持乱序执行,这将影响未来的优化策略;另一个是A53的流水线没有A57深,只有8级。

ARM v8a架构简介

异常等级

ARM v8a引入了异常等级的概念。一共有从EL0到EL3四种异常等级,等级越高,特权越高。我们的应用一般都运行于EL0。操作系统内核运行于EL1,EL2和EL3可以留给安全监控软件和KVM之类的虚拟化软件使用。

AArch64与AArch32

ARM芯片曾经指令集比x86容易学的重要原因是历史包袱少,不需要兼容历史上的指令集。现在ARM 64位芯片也不得不做起兼容自己以前的重任。ARM的做法是将运行状态分成AArch64和AArch32两种状态。AArch64就是我们后面重点学习的64位的指令集的运行态,而AArch32是兼容Arm-v7a的状态,所有Arm-v7a以及更早的软件都可以在这个状态上正常运行。

对于我们应用来讲,EL0是没有权限进行AArch64和AArch32状态切换的,所以我们只能一条道走到黑地用一处状态。这也是我们的A64指令无法切换到A32,T16指令的原因。寄存器

通用寄存器

在AArch64运行态下,在所有的异常级下,都可以访问31个64位通用寄存器,它们的命名是X0~X30。

这31个64位寄存器也可以通过W0~W30来访问低32位。读Wn时,不会影响到高32位的值。写Wn时,会将高32位全部清0.我们来看一段之前看过的例子:

str x0, [sp, #-32]!str lr, [sp, #24]str w1, [sp, #40]str w2, [sp, #44]

str x0是使用第0个64位寄存器。

str w1是只使用第1个64位寄存器的低32位特殊寄存器

- 零寄存器:XZR/WZR,写该寄存器会被忽略,读该寄存器会得到全0值。

- PC:程序指针寄存器,64位。注意,还是叫PC,不叫XPC啊!在ARMv7之前,PC可以做为R15,当成通用寄存器来使用,在ARMv8上,不允许直接访问。

- SP:栈寄存器,64位。对应的32位为WSP,但是64位的这个就叫SP不叫XSP啊!SP是每个EL对应一个(反正咱们只有EL0这个)。

- ELR(Exception Link Register):异常链接寄存器,EL1~EL3各有一个。存储了从中断返回的地址,这个咱们应用没权限用,本系列中学不到

- SPSR:(Saved Processor State):EL1~EL3各有一个。保存了发生异常时的状态信息,这个咱们也用不着。

状态域

在AArch64运行态下,没有对应CPSR(Current Program Status Register)的寄存器。每种状态现在需要分别访问。

这些状态有:

- N – 负数

- Z – 0

- C – 进位

- V – 溢出

- D – 调试位

- A – Serror

- I – IRQ

- F – FIQ

- SS – 软件单步跟踪

- IL – 无效运行态

- EL – Exception Level

- nRW – 执行态,0为64位,1为32位

- SP – 栈指针选择,0为EL0,n为ELn。

N, Z, C, V四种状态是可以在EL0级别被访问的,其它的都需要EL1以上级别。所以,咱们写应用只需要知道前4个就行了,多省心:)

系统寄存器

系统配置是通过MRS和MSR指令去访问系统寄存器来实现的。

NEON寄存器

在通用寄存器之外,ARMv8还提供了32个128位NEON浮点寄存器,V0~V31。它们也可以被当作半精度寄存器H,单精度寄存器S和双精度寄存器D。

A64 ATPCS支持最多传8个参数,通过X0~X7。而A32和T32只支持4个。说人话就是,如果一个函数调用要传8个参数,就可以放到X0~X7这8个64位寄存器里。

ARM v8a小结

ARM v8a支持AArch64和AArch32两种运行态,在应用运行的EL0权限下不能切换,只能选一种。AArch64状态下只能运行A64这一种指令集,而AArch32运行态下,可以执行A32和Thumb2两种指令集,这两种之间可以自由切换。

在AArch64运行态下,我们有31个64位通用寄存器(X0~X30),32个128位NEON浮点寄存器,一个零寄存器用于写无用数据,一个PC指令指针,一个SP栈指针,状态位只需要记4个:N负Z零C进行V溢出。

既然是快餐文,就讲这么多。大家能对上面小结的了解清楚,我们就可以正式向指令集前进了〜

转载地址:http://okdvx.baihongyu.com/